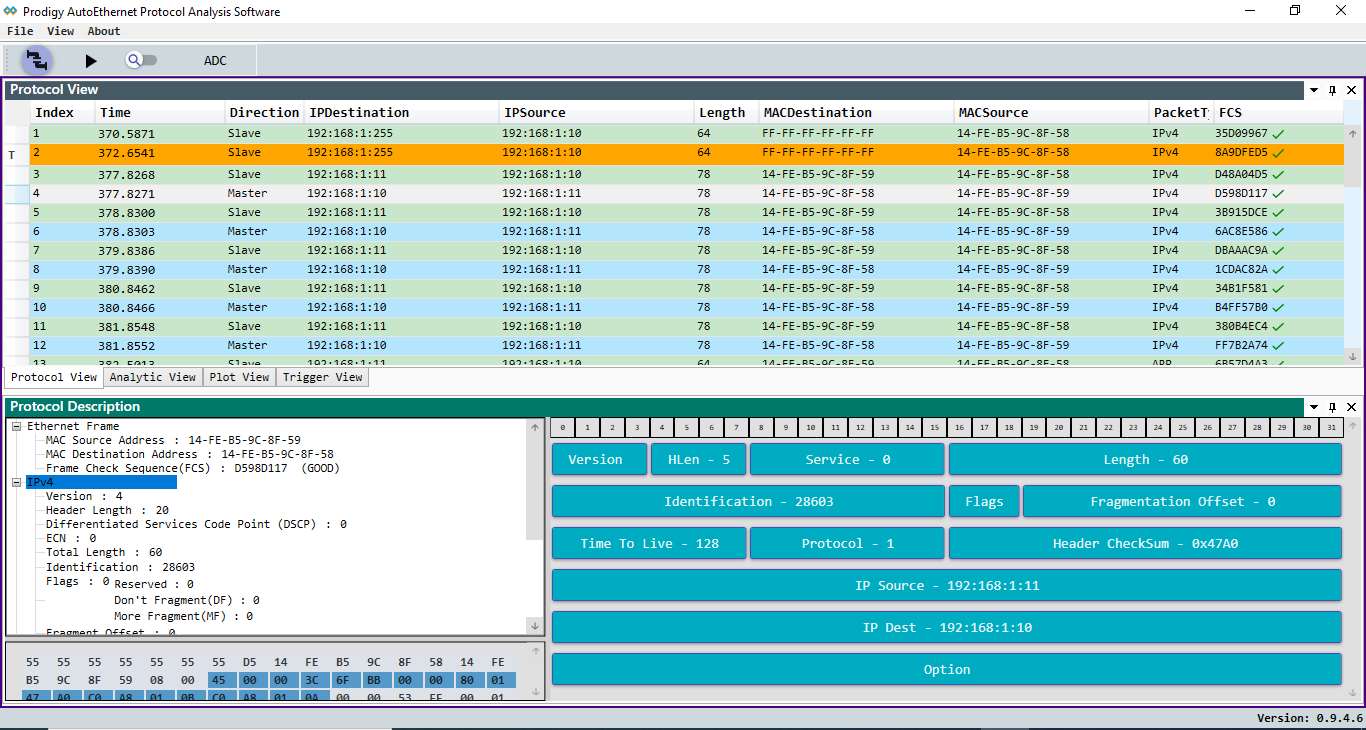

▶eMMC5.1/SD/SDIO protocol analyzer : PGY-SSM

PGY-SSM SD/SDIO/eMMC Protocol Analyzer is the comprehensive Protocol Analyzer with multiple features to capture and debug communication between host and memory under test. PGY-SSM Protocol Analyzer supports SD, SDIO and eMMC for data rates up to 200MHz (HS400) DDR mode. PGY-SSM is industry’s first eMMC protocol analyzer that supports version 4.41, 4.51, 5.0 and 5.1 specifications.

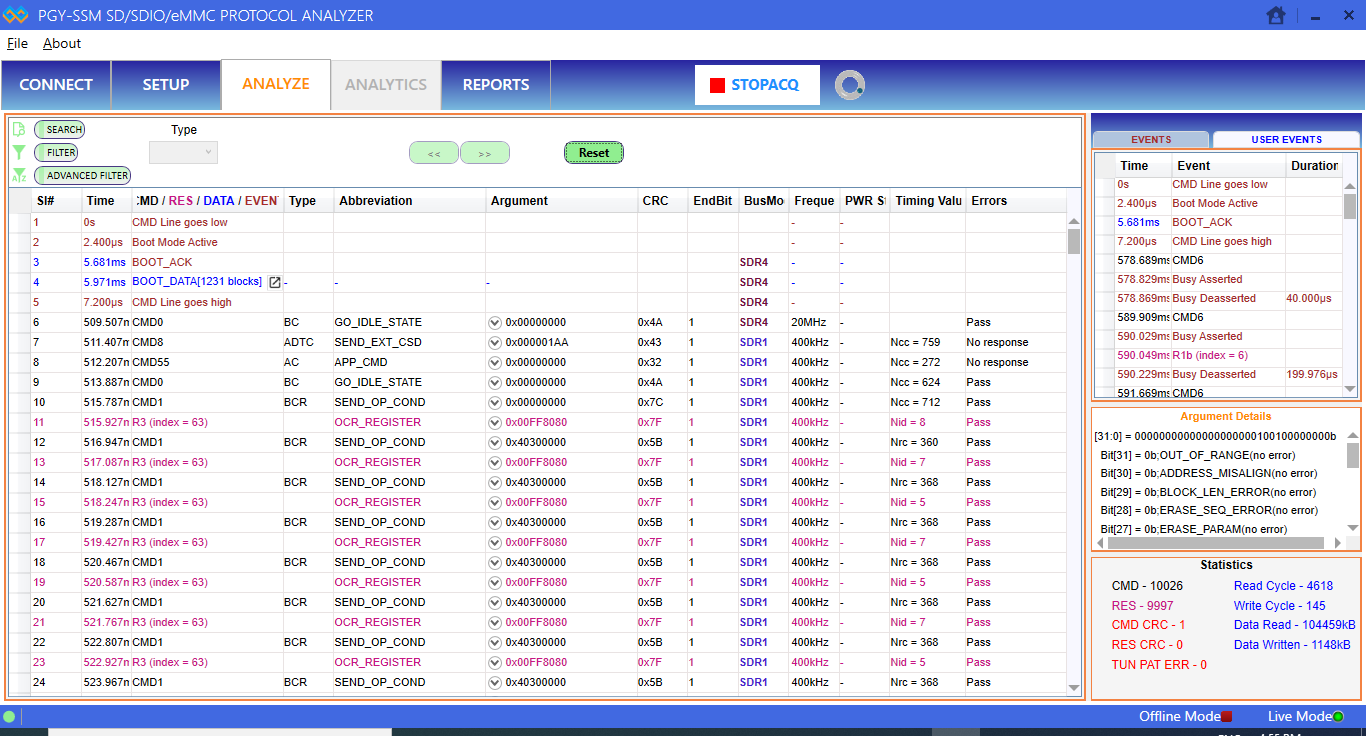

▶RFFE Exerciser & Protocol Analyzer : PGY-RFFE-EX-PD

The RF Front-end control interface (RFFE) Serial bus interface is emerging as a chosen for controlling RF frond end devices. There are variety of front end devices such as Power Amplifiers (PA), Low-Nose Amplifiers (LNA), filters, switches, power management modules, antenna tuners. It is widely used in mobile devices.

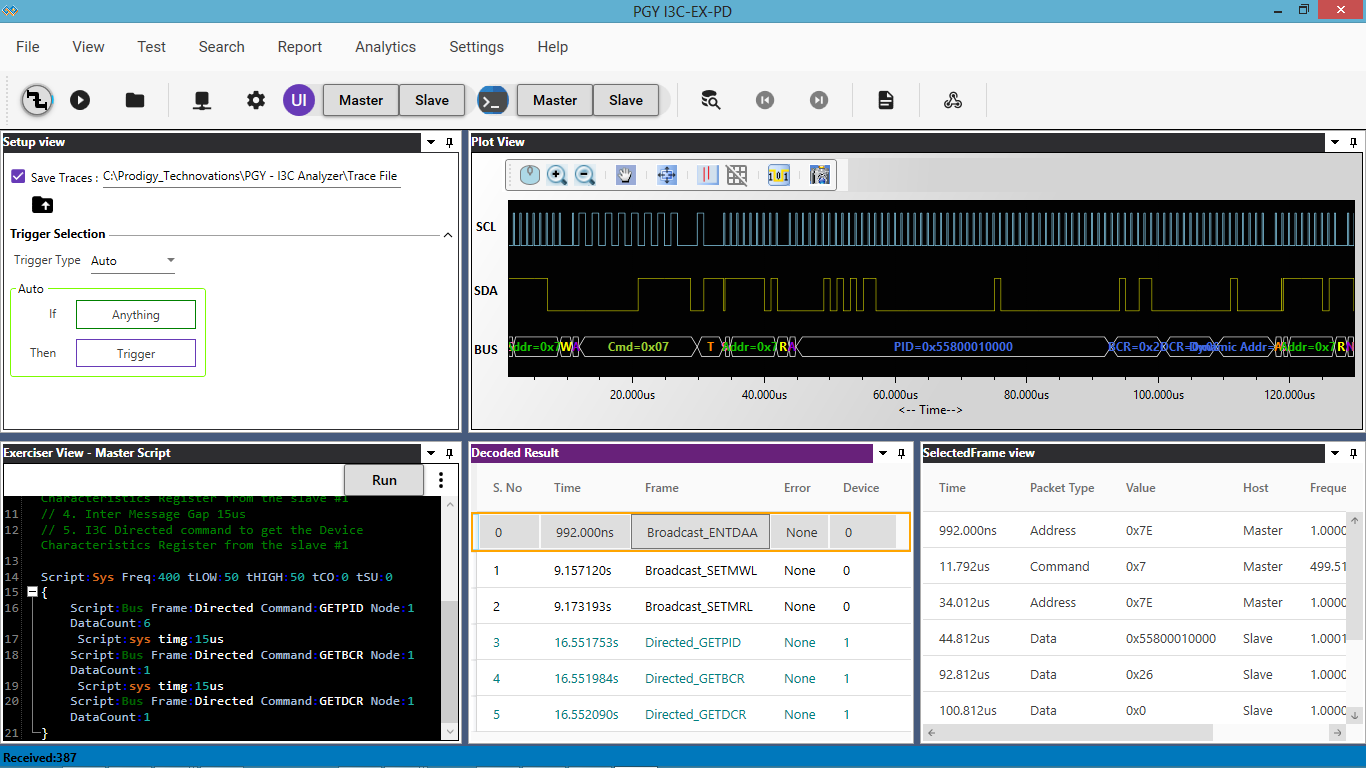

▶I3C PROTOCOL EXERCISER AND ANALYZER : PGY-I3C-EX-PD

I3C Serial bus interface is emerging as a chosen interface for all future sensor connectivity in mobile phone and automotive Industry. This could also be chosen for low cost, reliable interface for future embedded electronic applications to address the new data intensive applications.

PGY-I3C-EX-PD is the leading instrument that enables the design and test engineers to test the I3C designs for its specifications by configuring PGY-I3C-EX-ED as master/slave, generating I3C traffic with error injection capability and decoding I3C Protocol decode packets.

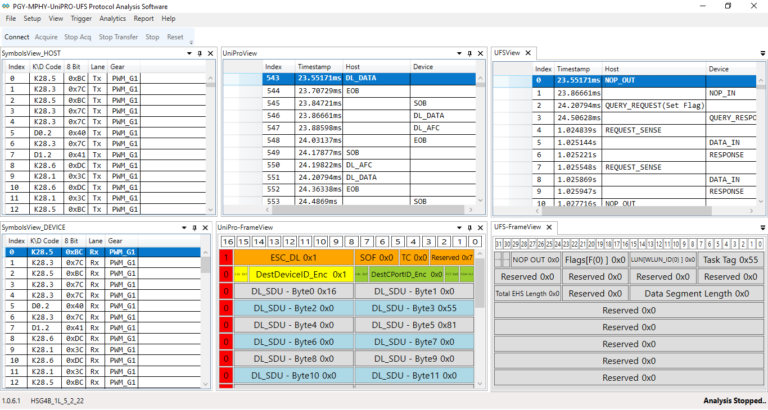

▶UFS2.1/3.0 Protocol Analyzer : PGY-UFS3.0-PA

PGY-UFS3.0-PA, UFS Protocol Analyzer, value based analyzer in its class, offers capture and debug of data across MPHY, UniPro and UFS protocol layers. It allows for instantaneous decoding of UFS layer, UniPro layer and MPHY layer with flexibility to correlate decoded data across these protocol layers.

PGY-UFS3.0-PA Supports PWMG1 to HSG4B data rates and two TX, two RX lane decode. The active probe has minimum electrical loading on device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS3.0-PA protocol Analyzer can support two lane data. Comprehensive decoding of data, protocol tests and error analysis enables validation of communication between UFS host and device.

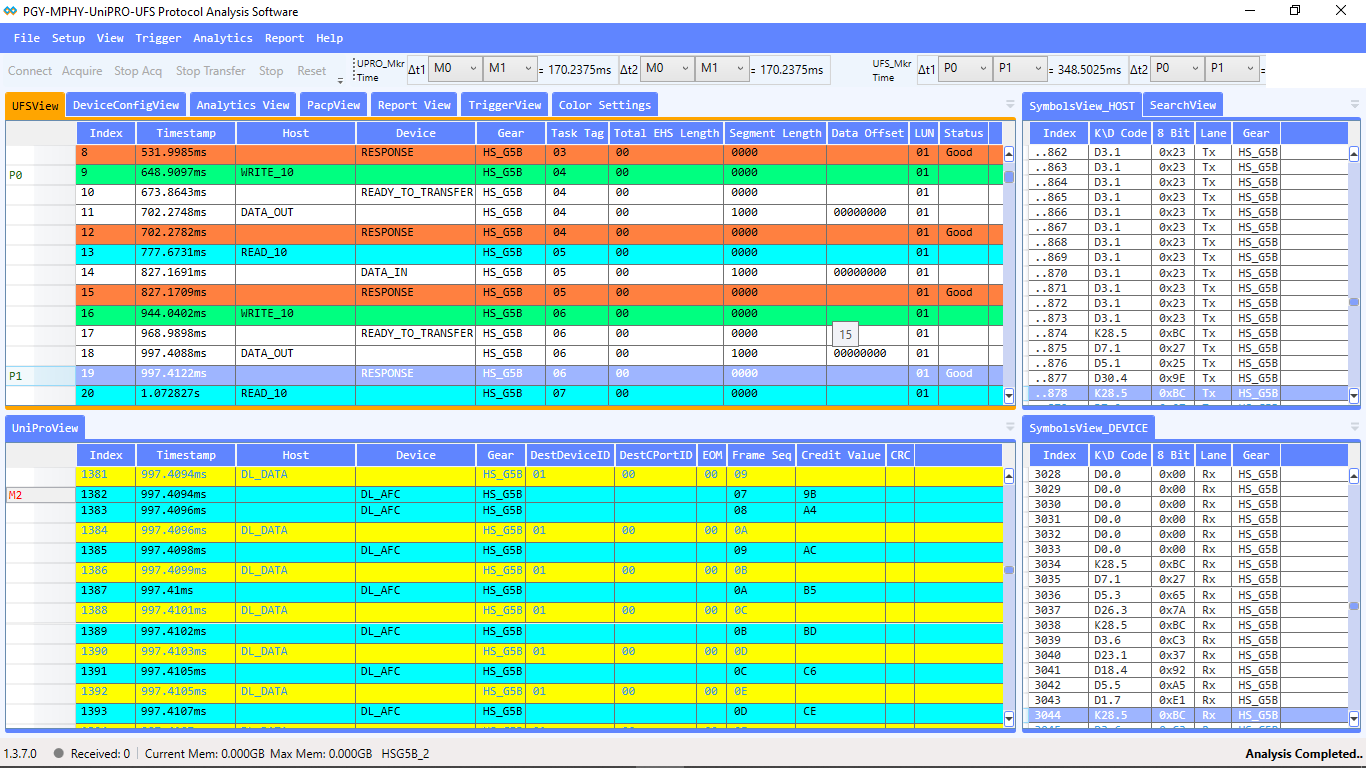

▶UFS4.0 Protocol Analyzer : PGY-UFS4.0-PA

PGY-UFS4.0-PA is the Protocol Analyzer with multiple features that offers protocol data capture and debug of data across MPHY, UniPro and UFS protocol layers. PGY-UFS4.X-PA, UFS Protocol Analyzer, allows for instantaneous decoding of UFS, UniPro and MPHY layers with flexibility to correlate decoded data across these protocol layers. PGY-UFS 4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS 4.0 Protocol Analyzer.

PGY-UFS4.0-PA supports PWMG1 to HSG5B data rates and two TX, two RX lane decode. The active probe has minimum electrical loading on device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS 4.0- PA Protocol Analyzer support two lane data. Comprehensive on the fly decoding of UniPro & UFS data enables validation of communication between UFS host and device.

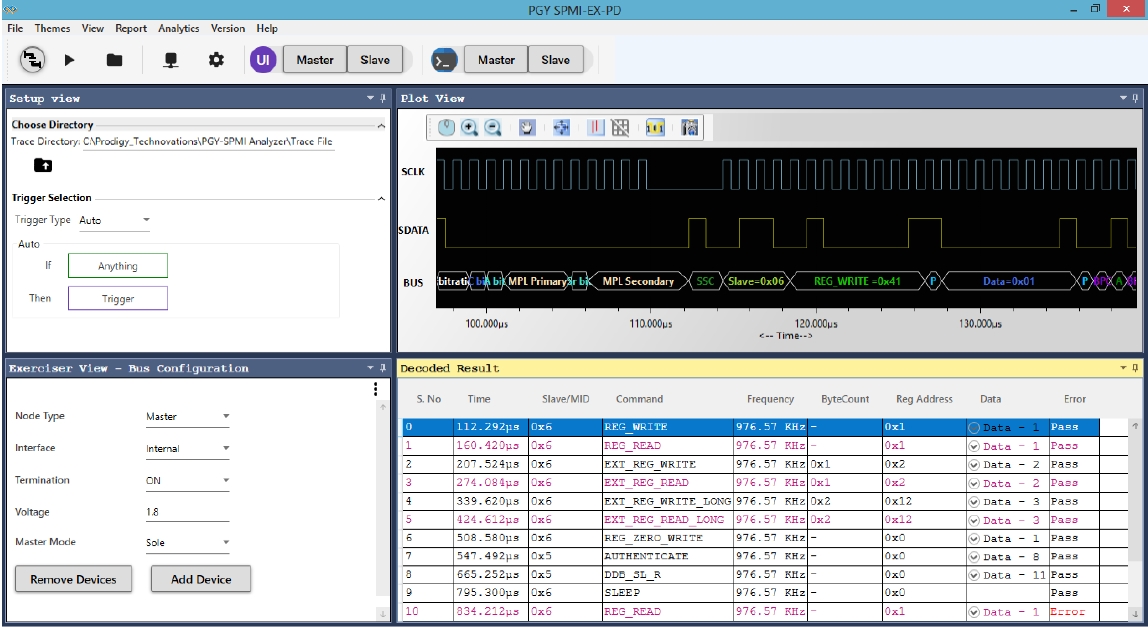

▶SPMI Protocol Exerciser and Analyzer : PGY-SPMI-EX-PD

SPMI (System Power Management Interface) is a MIPI (Mobile Industry Processor Interface) standard with 2-wire synchronous serial, bidirectional interface that connects the integrated Power Controller(PC) of a System-on-Chip (SoC) processor system with one or more Power Management Integrated Circuits (PMIC) voltage regulation systems.

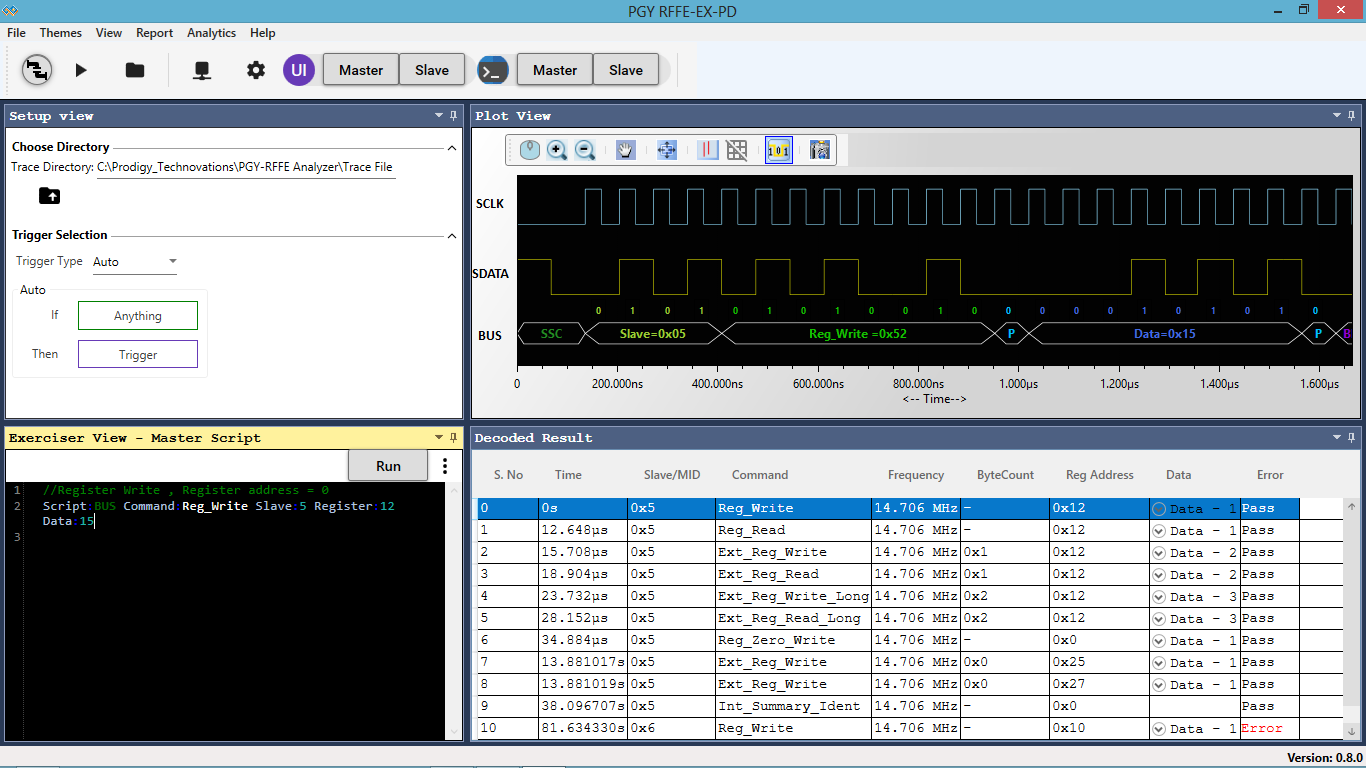

▶100BaseT1 Automotive Ethernet Protocol Analyzer : PGY-100BASET1

Prodigy Technovations 100BaseT1 Automotive Ethernet Protocol Analyzer provides industry first solution for non-intrusively passive tap the 100BaseT1 bus at physical layer and ensure no latency and accurate capturing of protocol data. Powerful basic and multi-level layer 2 to layer 7 protocol trigger capabilities enables design engineer capture protocol activity at specific event. PGY-100BaseT1-PA supports continuous streaming of captured protocol data to host computer SSD/HDD enabling long duration capture.

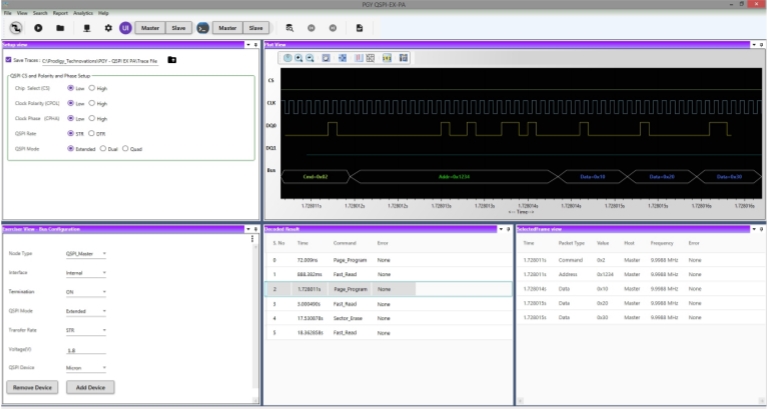

▶QSPI Protocol Exerciser and Analyzer : PGY-QSPI-EX-PD

QSPI Protocol Analyzer (PGY-QSPI-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-QSPI-EX-PD is the leading instrument that enables the design and test engineers to test the respective QSPI designs for its specifications by configuring the PGY-QSPI-EX-PD as Master/Slave, generating QSPI traffic and decoding the QSPI protocol decode packets.

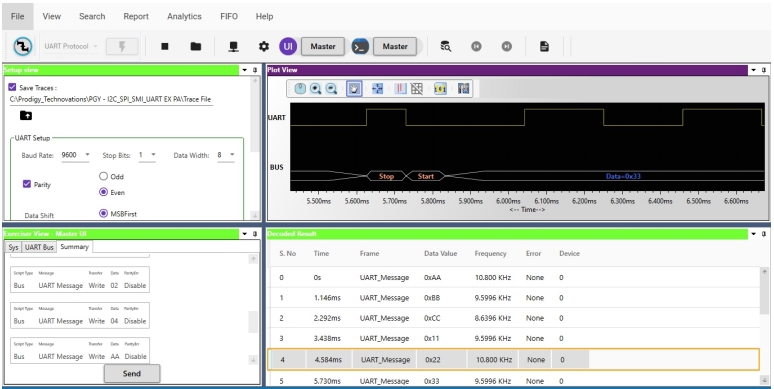

▶UART Protocol Exerciser and Analyzer : PGY-UART-EX-PD

UART Protocol Analyzer (PGY-UART-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-UART-EX-PD is the leading instrument that enables the design and test engineers to test the respective UART designs for its specifications by configuring the PGY-UART-EX-PD as Master/Slave, generating UART traffic and decoding the UART protocol decode packets.

UART stands for Universal Asynchronous Receiver Transmitter. A UART’s main purpose is to transmit and receive serial data. PGY-UART-EX-PD is the leading instrument that enables the design and test engineers to test the UART designs for its specifications. Generating UART traffic with custom traffic capability and decoding UART Protocol packets.

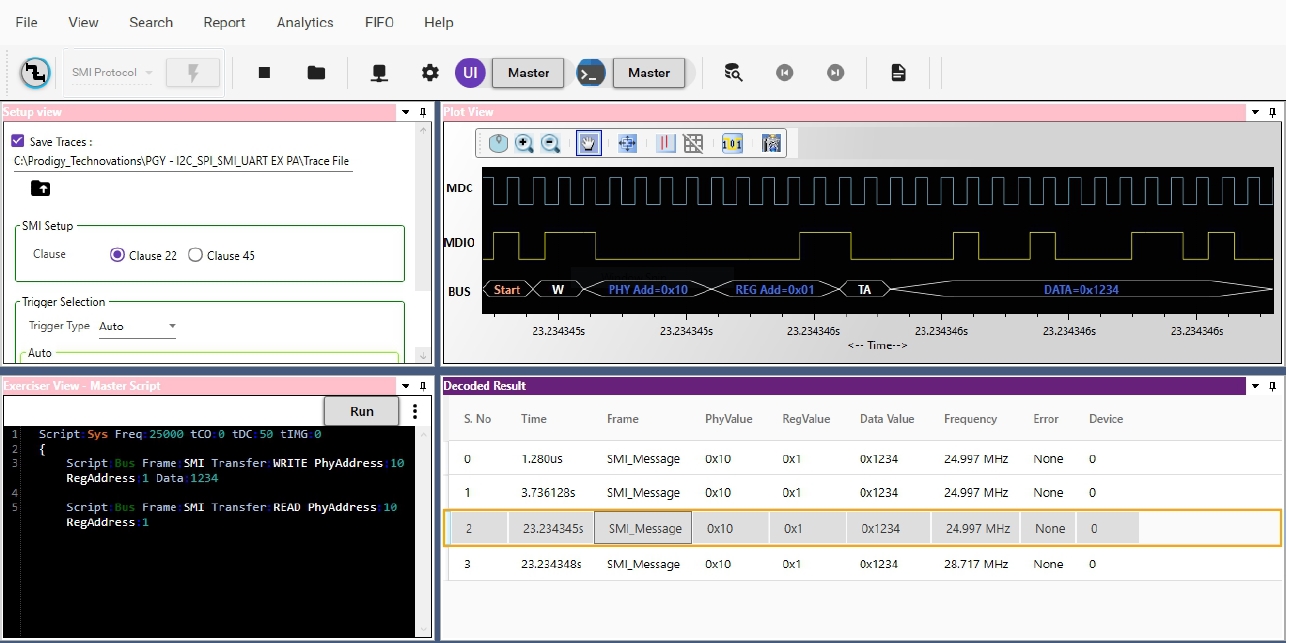

▶SMI Protocol Exerciser and Analyzer : PGY-SMI-EX-PD

SMI Protocol Analyzer (PGY-SMI-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-SMI-EX-PD is the leading instrument that enables the design and test engineers to test the respective SMI designs for its specifications by configuring the PGY-SMI-EX-PD as Master/Slave, generating SMI traffic and decoding the SMI protocol decode packets.

SMI also called as Management Data Input/Output, or MDIO, is a 2-wire serial bus that is used to manage physical layer devices in media access controllers (MACs) in Gigabit Ethernet equipment. The management of these PHYs is based on the access and modification of their various registers.

PGY-SMI-EX-PD is the leading instrument that enables the design and test engineers to test the SMI designs for its specifications by configuring PGY-SMI -EX-PD as master/slave, generating SMI traffic with error injection capability and decoding SMI Protocol packets.

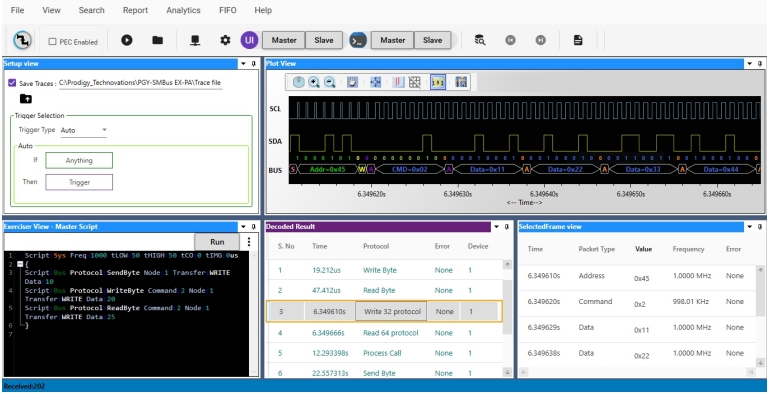

▶SMBus Protocol Exerciser and Analyzer : PGY-SMBus-EX-PD

SMBus Protocol Analyzer (PGY-SMBus-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-SMBus-EX-PD is the leading instrument that enables the design and test engineers to test the respective SMBus designs for its specifications by configuring the PGY-SMBus-EX-PD as Master/Slave, generating SMBus traffic, and decoding the SMBus protocol decode packets.

SM Bus Serial bus interface has been widely used for voltage and temperature monitoring of the system.

PGY-SMBus-EX-PD is the leading instrument that enables the design and test engineers to test the SM Bus designs for its specifications by configuring PGY-SM Bus -EX-PD as master/slave, generating SM Bus traffic with error injection capability, and decoding SM bus Protocol decode packets. SM Bus Serial bus interface has been widely used for voltage and temperature monitoring of the system.

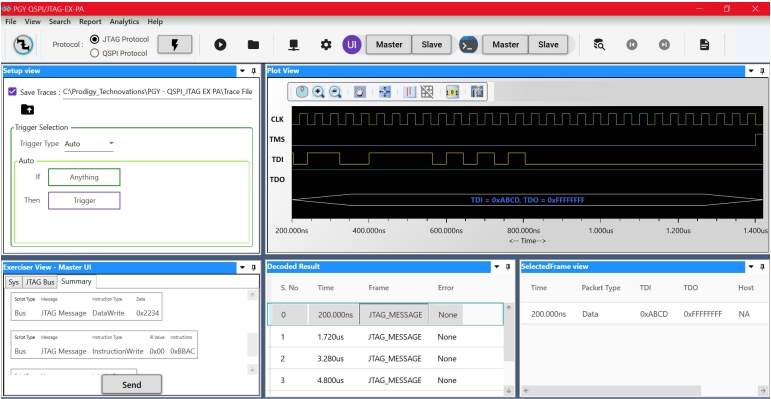

▶JTAG Protocol Exerciser and Analyzer : PGY-JTAG-EX-PD

JTAG Protocol Analyzer (PGY-JTAG-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-JTAG-EX-PD is the leading instrument that enables the design and test engineers to test the respective JTAG designs for its specifications by configuring the PGY-JTAG-EX-PD as Master/Slave, generating JTAG traffic and decoding the JTAG protocol decode packets.

PGY-JTAG-EX-PD is the leading instrument that enables the design and test engineers to test the JTAG designs for its specifications by configuring PGY-JTAG-EX-PD as master/slave, generating JTAG traffic with error injection capability and decoding of JTAG Protocol packets.

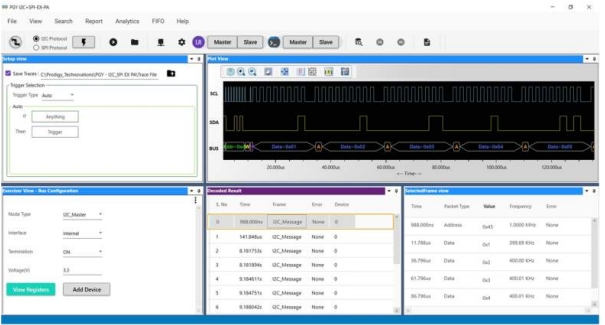

▶I2C/SPI Protocol Exerciser and Analyzer : PGY-I2C/SPI-EX-PD

I2C Protocol Analyzer and SPI Protocol Analyzer(PGY-I2C/SPI-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-I2C/SPI-EX-PD is the leading instrument that enables the design and test engineers to test the respective I2C or SPI designs for its specifications by configuring the PGY-I2C/SPI-EX-PD as Master/Slave, generating I2C/SPI traffic and decoding the I2C/SPI protocol decode packets.

I2C is a two-wire interface to connect low speed devices like micro-controllers, EEPROM’s, A/D & D/A converters, I/O interfaces, and other small peripherals in embedded systems. I2C bus is used by many IC’s and is simple to implement. Any microcontroller can communicate with I2C buses. I2C bus can communicate in slow devices and can also use high speed modes to transfer large amounts of data.

SPI is one of the widely used interfaces between micro-controller and peripheral IC’s such as sensors, ADC’s, DAC’s, shift registers, SRAM, and others. SPI is synchronous, full-duplex master-slave based interface. Both master and slave can transmit data at the same time. The SPI interface can be a 3 wire or 4-wire.

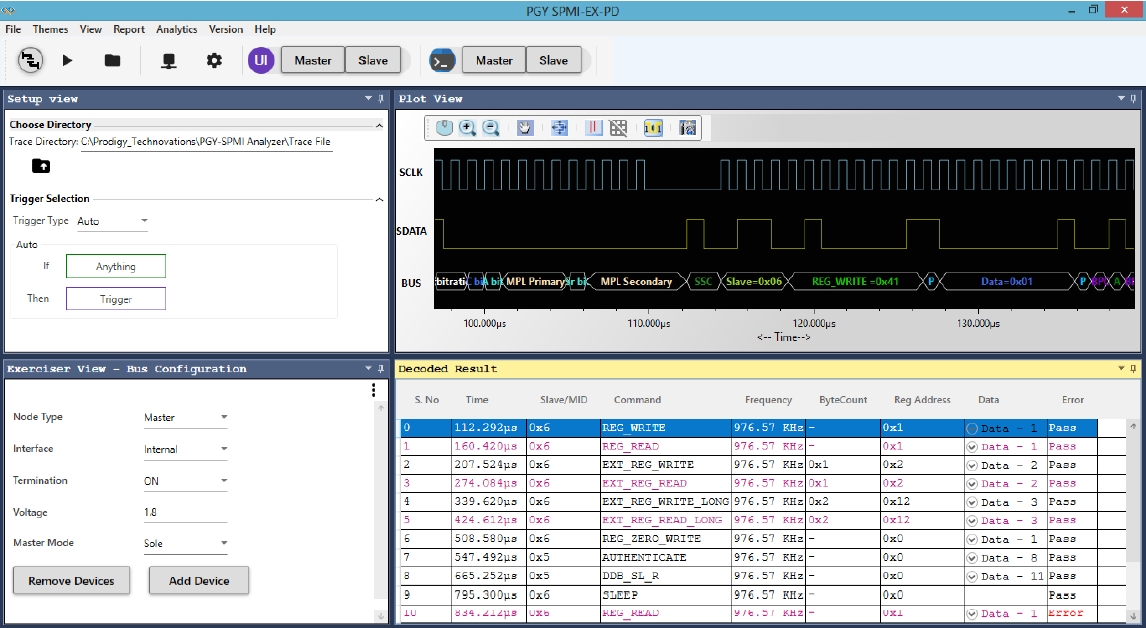

▶SPMI Protocol Exerciser and Analyzer : PGY-SPMI-EX-PD

SPMI Protocol Analyzer(PGY-SPMI-EX-PD) is the Protocol Analyzer with multiple features to capture and debug communication between host and design under test. SPMI (System Power Management Interface) is a MIPI (Mobile Industry Processor Interface) standard with 2-wire synchronous serial, bidirectional interface that connects the integrated Power Controller(PC) of a System on- Chip (SoC) processor system with one or more Power Management Integrated Circuits (PMIC) voltage regulation systems.

PGY-SPMI-EX-PD is the leading instrument that enables the design and test engineers to test the SPMI designs for its specifications by configuring PGY-SPMI-EX-ED as master/slave, generating SPMI traffic with time variation and error injection capability and decoding SPMI Protocol packets.

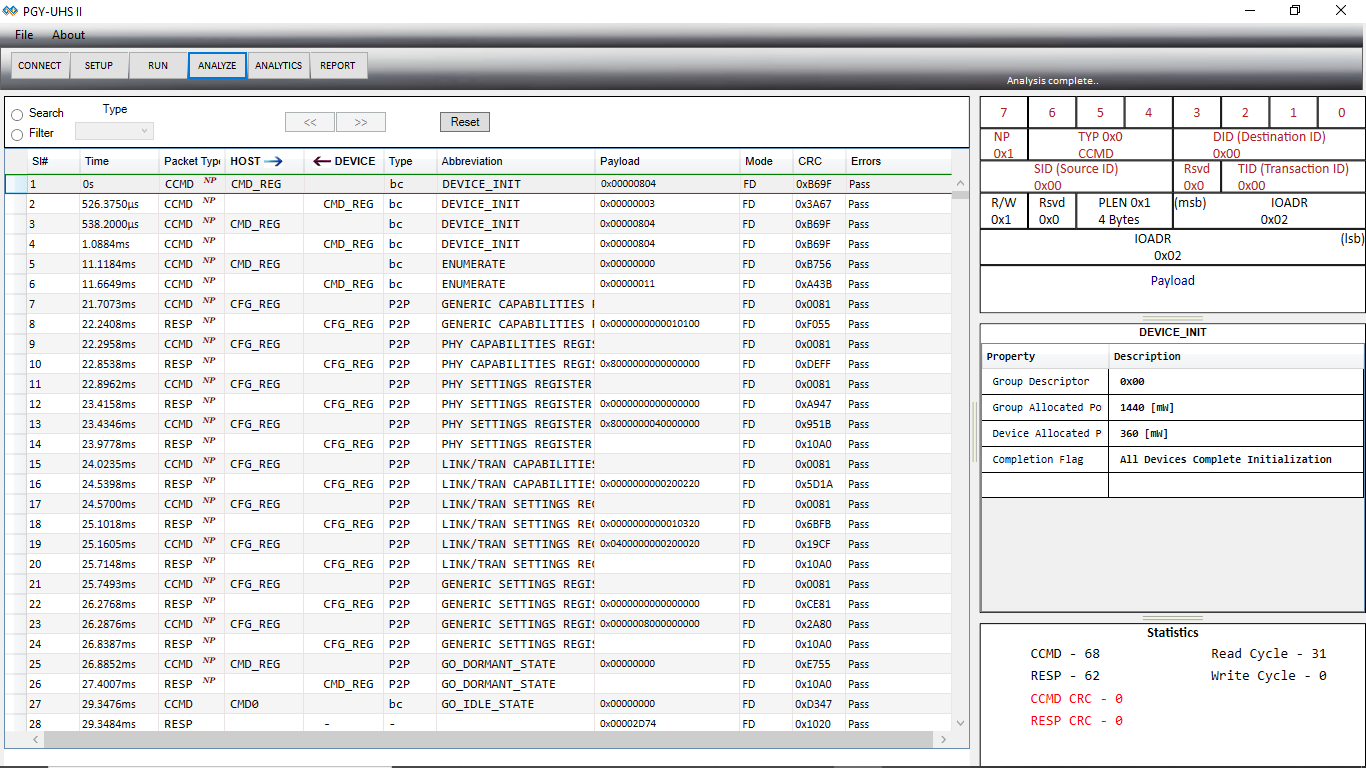

▶SD/SDIO UHS II Protocol Analyzer : PGY-UHS II

PGY-UHS II SD/SDIO UHS II Protocol Analyzer is the most feature rich comprehensive Protocol Analyzer available to capture and debug UHS-II protocol data. PGY-UHS-II Protocol Analyzer supports FD156 and HD312 data rate. The innovative active probe has minimum electrical loading on device under test (DUT) and captures protocol data without affecting the performance of DUT.

Prodigy Technovations Pvt. Ltd.

South Korea Authorized Distributor, 한국총판