프로토콜 디코딩 기능이있는 DISCOVERY 시리즈 PGY-LA-EMBD 로직 분석기는 소비자, 산업, 가정 자동화, 건강 및 교육 부문의 임베디드 설계 팀이 직면한 로직 및 프로토콜 문제를 디버깅하도록 설계되었습니다.

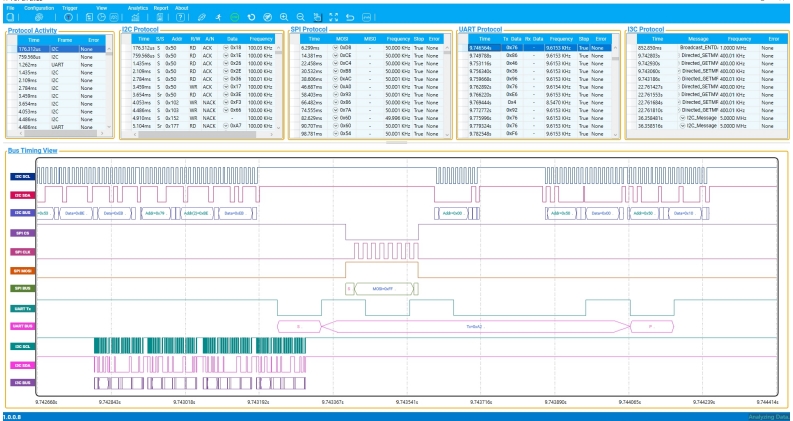

PGY-LA-EMBD는 엔지니어가 타이밍 문제를 디버깅하고 임베디드 설계에서 I2C, I3C, SPI, UART, SPMI 및 RFFE 인터페이스의 동시 프로토콜 분석을 수행 할 수있는 업계 최초의 로직 분석기입니다. 이를 통해 설계자는 회로 수준 및 시스템 수준 문제를 신속하게 디버깅 할 수 있습니다.

[Logic Analyzer for Embedded Interfaces Data Sheet]

PGY-LA-EMBD는 1GS/sec 비동기 (타이밍) 데이터 및 100Mhz 동기 (상태) 데이터 캡처를 제공하므로 디지털 설계 문제를 해결하는 데 이상적인 디버그 도구입니다. 이제 설계자는 프로토콜 문제 분석과 별도로 설정 및 보류 시간 문제, 결함 및 동기 데이터 활동을 쉽게 분석 할 수 있습니다.

현재 세대의 임베디드 설계자는 >I2C, I3C, SPI, UART, SPMI 및 RFFE와 같은 여러 인터페이스에서 데이터를 수집하고 이를 처리하여 설계의 최적 성능을 달성해야합니다. 임베디드 디자인 팀은 제품의 의도 된 목표를 충족하기 위해 적시에 조치를 취해야합니다. PGY-LA-EMBD는 >I2C, I3C, SPI, UART, SPMI 및 RFFE 버스를 동시에 디코딩하고 타임 스탬프 정보와 함께 프로토콜 활동을 표시합니다.

PGY-LA-EMBD는 하드웨어 및 임베디드 소프트웨어 통합 문제를 디버깅하고 소프트웨어 성능을 최적화하는 데 이상적인 장비입니다.

여러 마커를 사용하면 설계자에게 중요한 스마트 델타를 측정하고, Zoom을 사용하면 사용자가 신호의 특정 영역을 볼 수 있습니다.

Features

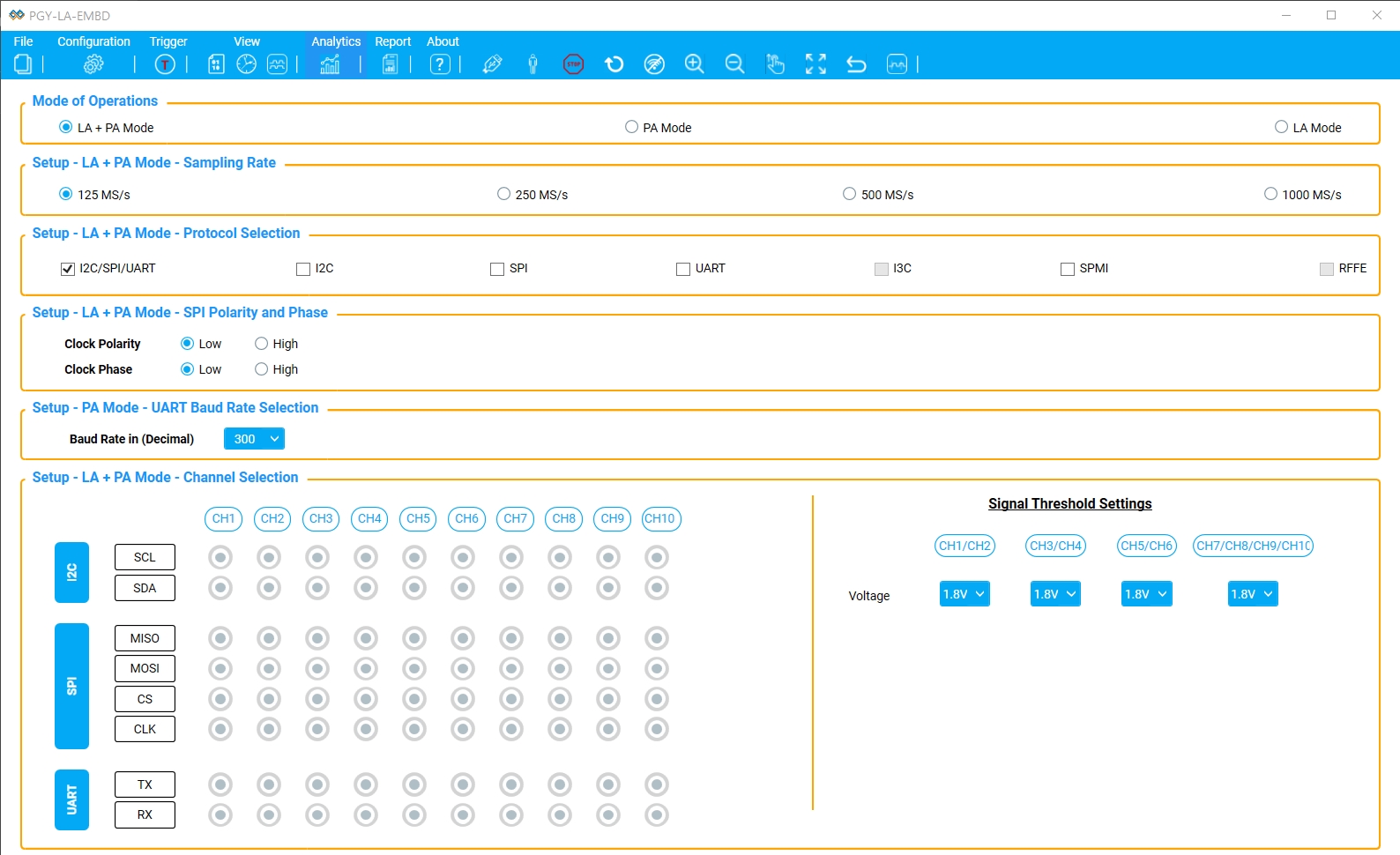

- 16 channels with Protocol and Logic Analysis capability.

- 1GS/Sec Timing (Asynchronous) Analysis

- 100MHz State (Synchronous) Analysis

- Simultaneous Protocol Analysis of UART, SPI and I2C.

- Detailed Trigger capabilities: Auto, Pattern, Protocol aware (UART, SPI and I2C) and timing (pulse width and delay).

- Smart streaming of data from Protocol. Analyzer to host computer for long duration capture using USB3 interface.

- Innovative easy to use Graphical user interface.

- Error Analysis of Protocol packet

- Provides timing, waveform, listing and Protocol listing views

- Detailed filtering capability for protocol decoded data

- PDF and CSV report format.

- API support.

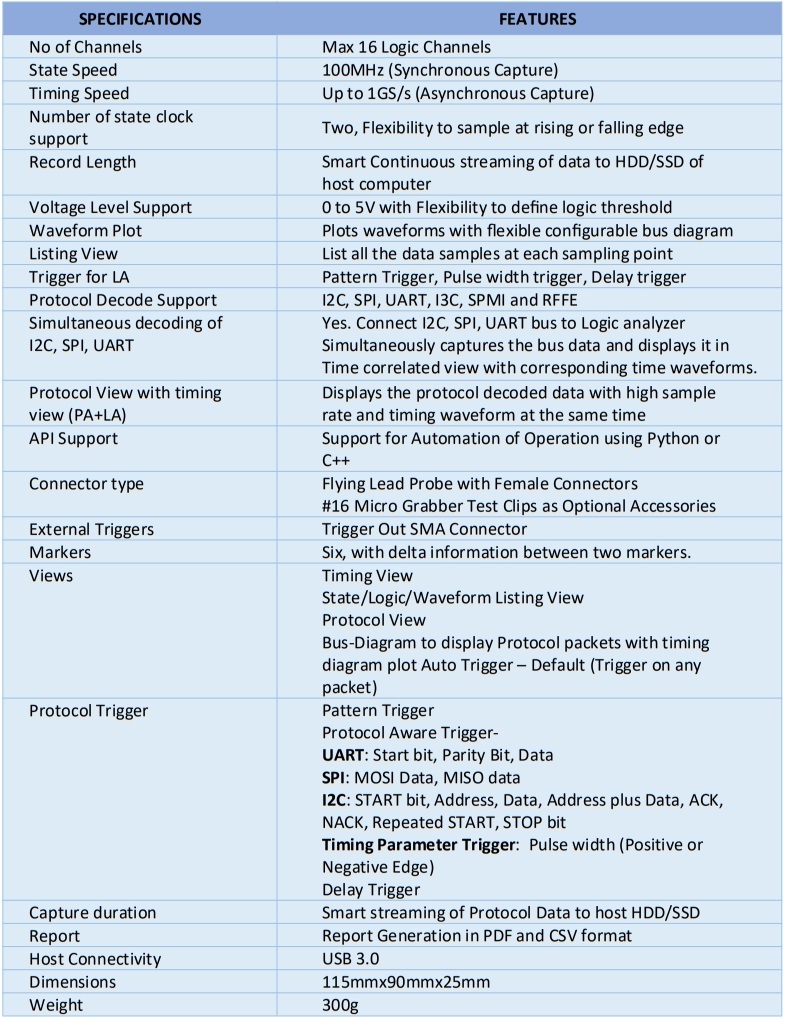

Specification