# PGY-SPMI-EX-PD SPMI Protocol Exerciser & Analyzer

SPMI Protocol Exerciser & Analyzer

SPMI (System Power Management Interface) is a MIPI (Mobile Industry Processor Interface) standard with 2-wire synchronous serial, bidirectional interface that connects the integrated Power Controller (PC) of a System-on-Chip (SoC) processor system with one or more Power Management Integrated Circuits (PMIC) voltage regulation systems.

PGY-SPMI-EX-PD is the leading instrument that enables the design and test engineers to test the SPMI designs for its specifications by configuring PGY-SPMI-EX-ED as master/slave, generating SPMI traffic with error injection capability and decoding SPMI Protocol decode packets.

#### **Features:**

- Support SPMI v 1.0 or 2.0 specifications

- Ability to configure it as Master or Slave

- Supports Request Capable Slave (RCS) feature

- Generate different SPMI Packets

- Error injection such as parity error, ACK/NACK error and Skip SSC error

- Variable SPMI data speeds (32kHz 26Mhz)

- Simultaneously generate SPMI traffic and Protocol decode of the Bus

- Timing diagram of Protocol decoded bus

- Listing view of Protocol activity

- Error Analysis in Protocol Decode

- Ability to write exerciser script to combine multiple data frame generation at different data speeds

- USB2/3 host computer interface

- Continuous streaming protocol activity to host system HDD/SSD

- API support for automation in Python or C#

- Flexibility to upgrade to the unit for evolving SPMI Specification

- Optional Protocol Implementation Compliance Statement (PICS) support scripts

### **Product Setup**

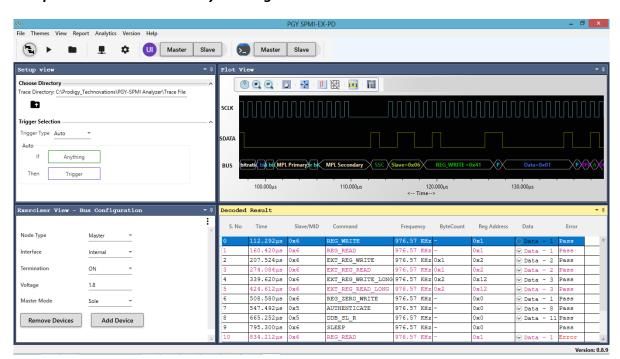

### Comprehensive Protocol Analysis using Multi-View

Multidomain View provides the complete view of SPMI Protocol activity in single GUI. User can easily setup the analyzer to generate SPMI traffic using a GUI or script. User can set different trigger conditions from the setup menu to capture Protocol activity at specific event and decode the transition between Master and Slave. The decoded results can be viewed in timing diagram and Protocol listing window with autocorrelation. This comprehensive view of information makes it industry best, offering an easy to use solution to debug the SPMI protocol activity. Continuous streaming protocol activity to host system HDD/SSD ensures seamless roll mode operation without the need to recapture data when DUT/s are set to different states thereby saving test times.

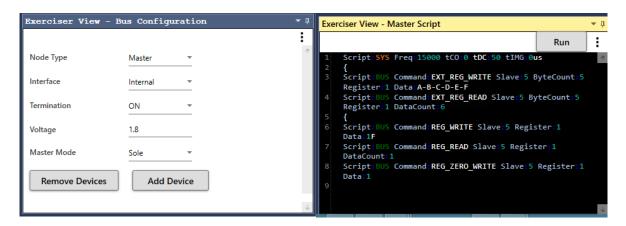

#### Exerciser:

PGY-SPMI-EX-PD supports SPMI traffic generation using GUI and Script. User can generate simple traffic generation using the GUI to test the DUT. Script based GUI provides flexibility to emulate the complete expected traffic in real world including error injections. In this sample script user can generate SPMI traffic as below.

Script line #3: Ext Reg Write to the slave with USID 05 Script line #4: Ext Reg Read to the slave with USID 05 Script line #6: Reg Write to the slave with USID 05 Script line #7: Reg Read to the slave with USID 05

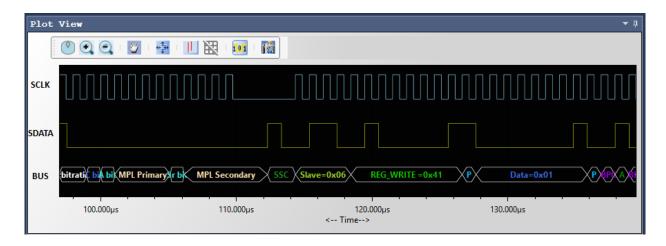

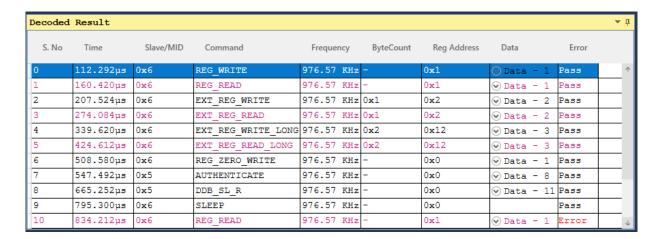

#### **Timing Diagram and Protocol Listing View**

Timing view provides the plot of SCL and SDA signals with bus diagram. Overlaying of Protocol bits on the digital timing waveform will help easy debugging of Protocol decoded data. Cursor and Zoom features will make it convenient to analyze Protocol in timing diagram for any timing errors.

Protocol window provides the decoded packet information in each state and all packet details. Selected frame in Protocol listing window will be auto correlated in timing view to view the timing information of the packet.

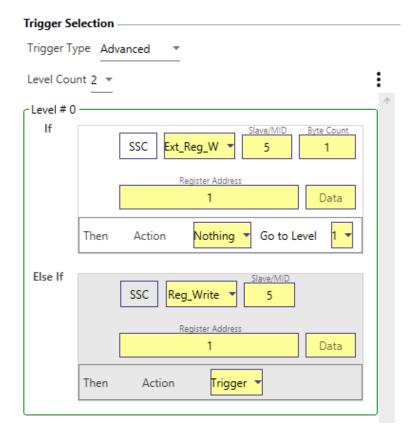

#### **Powerful Trigger Capabilities**

PGY-SPMI-EX-PD supports simple trigger capabilities. Analyzer can trigger on any of the Protocol packets such as Reg Write, SLEEP or WAKE UP. Advanced Trigger provides the flexibility to monitor Multiple trigger conditions and can set multiple state trigger machine. User can initiate a timer and trigger on set timer values.

| PGY-SPMI-EX-PD Specification | Features                                                                                                                         | PGY-SPMI-EX-PD |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|

|                              |                                                                                                                                  |                |

| Exerciser:                   |                                                                                                                                  |                |

| Configurable                 | 1 Master + 2 Slaves                                                                                                              | ~              |

| SPMI Traffic Generation      | Custom SPMI traffic generation                                                                                                   | ~              |

|                              | Simulate real world network traffic                                                                                              | ~              |

| SCL Frequency                | 32 kHz to 26 MHz                                                                                                                 | ~              |

| Voltage Drive Level          | 1.2V or 1.8V                                                                                                                     | ~              |

| Command sequence Support     | All command sequence is supported except DDB master Read                                                                         | ~              |

| SCLK Duty Cycle variation    | YES. (can be 25%, 50%, 75%)                                                                                                      | ~              |

| SCLK & SDATA Delay           | Resolution (4ns)                                                                                                                 | ~              |

| Delay between two messages   | YES                                                                                                                              | ~              |

| Specification                | SPMI 1.0 and SPMI 2.0                                                                                                            | ~              |

| SPMI network                 | Sole master and multi master                                                                                                     | ~              |

| Error injection              | Master - Data parity, - command parity, - address parity - Skip SSC (only in Sole master systems)  Slave - Data parity (NON RCS) | -              |

| Protocol Analysis:           |                                                                                                                                  |                |

| Supports                     | SPMI protocol decode                                                                                                             |                |

| Protocol Views               | Timing Diagram View Protocol Listing View Bus-Diagram to display Protocol packets with timing diagram plot                       | ~              |

| Protocol Trigger             | Simple (Trigger on user defined SPMI packet after SSC)                                                                           | ~              |

| Capture Duration             | Continuous streaming Protocol Data                                                                                               | ~              |

| Protocol Error Report        | Data parity, command parity, address parity ACK/ NACK error                                                                      | ~              |

| Host Connectivity            | USB 3.0 / 2.0 interface                                                                                                          | ~              |

# **Ordering Information**

PGY-SPMI-EX-PD SPMI Protocol Exerciser and Analyzer (Please mention the specification needed)

-Opt PICS (Protocol Implementation Compliance Statement test scripts)

(Please Specify version to be supported V1.0/V2.0)

# Deliverables for PGY-SPMI-EX-PD

PGY-SPMI-EX-PD Unit

USB3.0 cable

PGY-SPMI-EX-PD Software in CD

12V DC adopter

Flying lead probe cable with female connector to connect to DUT

# **Contact Information**

| Address:           | Prodigy Technovations Pvt Ltd                     |

|--------------------|---------------------------------------------------|

|                    | 294, 7 <sup>th</sup> Cross, 7 <sup>th</sup> main, |

|                    | BTM 2 <sup>nd</sup> Stage,                        |

|                    | Bengaluru – 560076.                               |

|                    | Karnataka                                         |

|                    | India.                                            |

| Website:           | www.prodigytechno.com                             |

| Technical Support: | <u>contact@prodigytechno.com</u>                  |

|                    |                                                   |

| Phone:             | +91-80-42126100                                   |

|                    |                                                   |

#### About Prodigy Technovations Pvt Ltd

Prodigy Technovations Pvt Ltd (www.prodigytechno.com) is a leading global technology provider of Protocol Decode, and Physical layer testing solutions on test and measurement equipment. The company's ongoing efforts include successful implementation of innovative and comprehensive protocol decode and physical Layer testing solutions that span the serial data, telecommunications, automotive, and defense electronics sectors worldwide.